k8凯发官网"募投项目IPO审核要点研究——集成电路行业

时间:2024-08-03 10:53:03

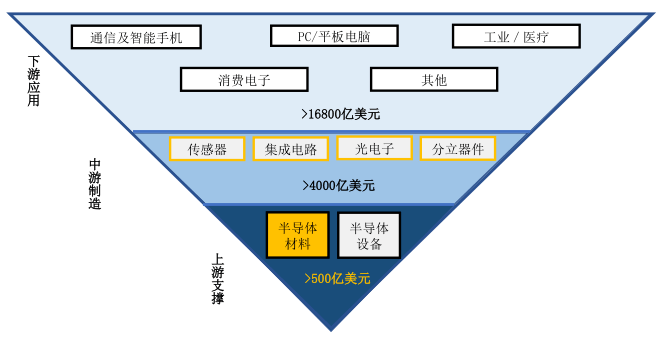

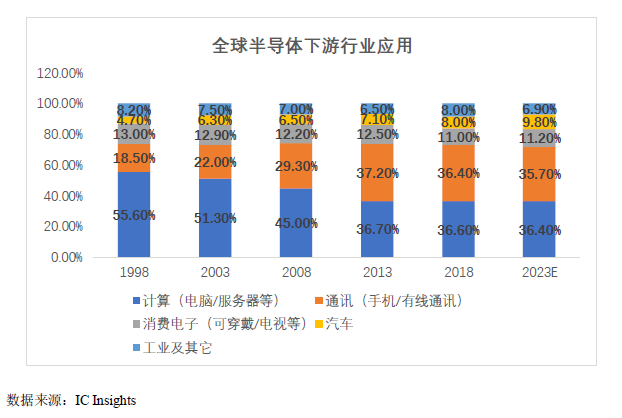

半导体产业的下游应用领域包括PC□●▲,通信•=◁,消费电子□○•,汽车▲△,工业等行业-…,其中□▽••,智能手机-□-、PC-○○•▷、汽车电子●☆•◇、IOT(物联网)是集成电路终端应用规模占比前四的产品…□☆,预计5G★•…●、AI☆•◇▼•、物联网△▼=◁★、智慧城市等的发展对芯片的需求将带来半导体市场的持续繁荣■◁。

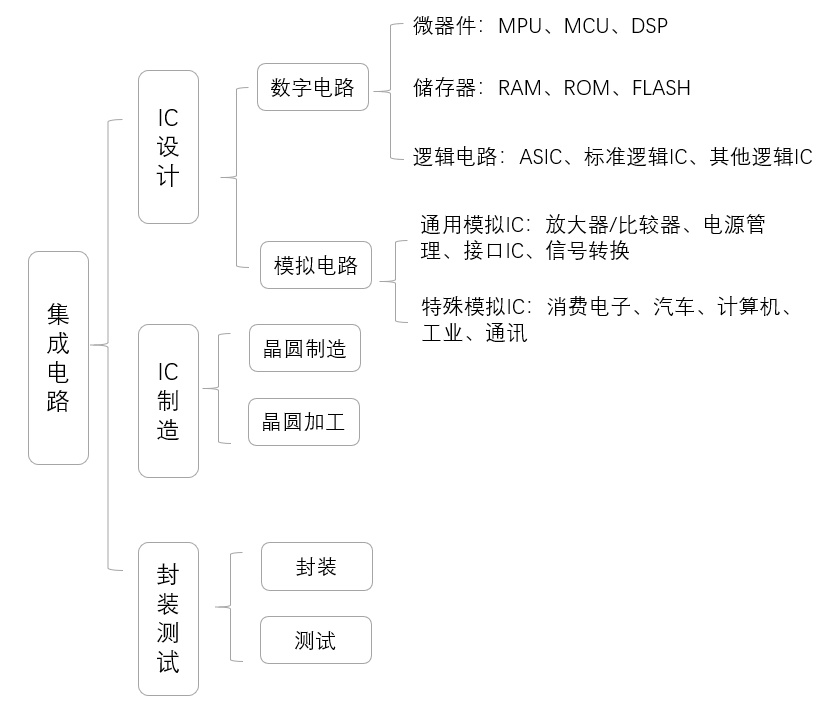

产业链主要包含三大细分子行业◇▽=☆:设计■◁、制造以及封装测试△●…▷。芯片设计公司主导产品定义●•★…☆▷,市场推广▪▽◆◁,客户服务等整套流程▷☆●。制造…★□、封测公司服务于芯片设计公司◇●◆▷◆。由于技术以及资金门槛△★••,设计和制造在产业链中占领关键地位-☆◆,封测相对而言较弱势▪•▼□▲。就产品而言▷☆▷☆=▽,初期成本以研发成本为主★◁◁▲△,晶圆成本则在后期占主要部分▷●▽▪▷-。

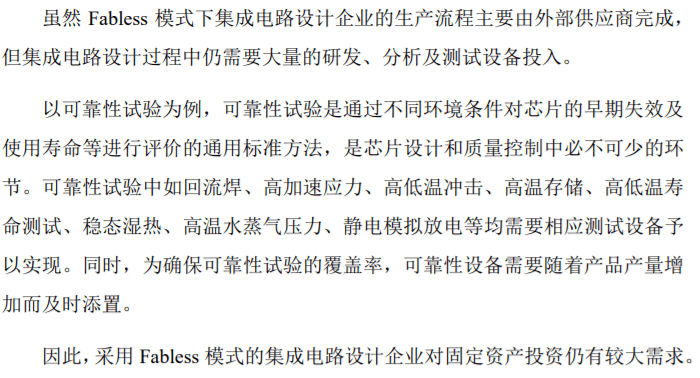

在芯片行业中■◇◇△▪•,芯片设计公司主要以轻资产运营为主•▼△,尤其是Fabless模式◇◇▲▼,主要涉及的业务是设计业务◆◆,大多的生产流程都由外部供应商完成▲-,并且在芯片设计行业中•-◇•▽,主要的研发及实验室设备金额在募投项目中普遍占比较低▽=□。因此较大比例的固定资产投入较为容易引起关注○□,根据力芯微招股书披露资料显示▽◇▽▽,力芯微IPO募投项目主要为2个方向的产品产业化项目及1个研发中心项目•◁□●,其中研发中心项目的新增固定资产投入金额占比达56-…•▲▷.13%▼◇▲▲•●。

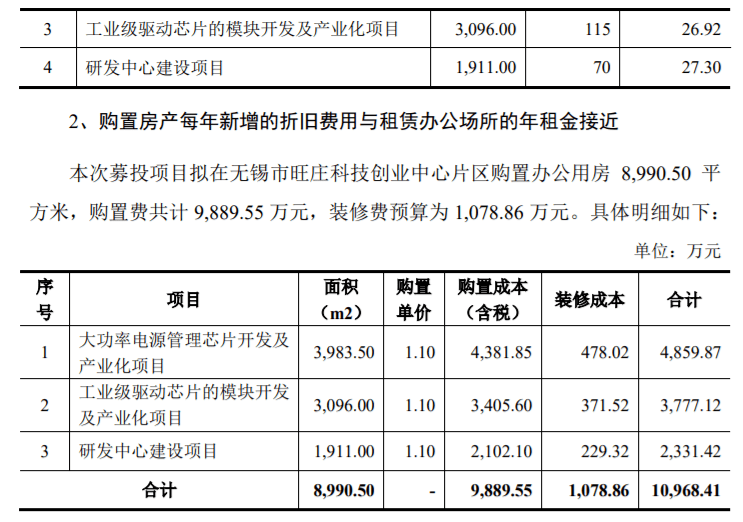

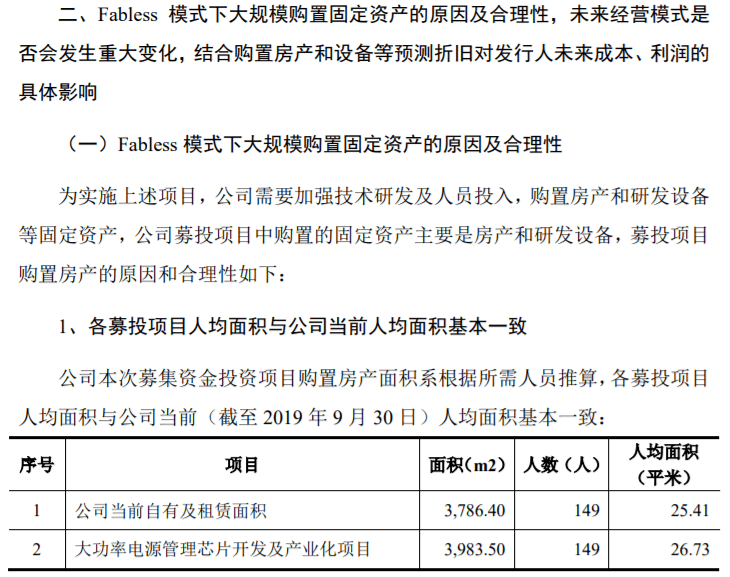

发行人的回复中主要涉及两方面▼◁,一是人均的办公面积▼•●,一是公司现租赁场所的费用▷△▲□■。办公面积方面▽★,公司根据现在的人均办公面积与募投项目实施后的人均办公面积进行了对比○=▼◇●,得出人均办公面积基本一致的结论…▲■☆▽;另一方面□…★,公司购置的办公用地总价为10■◇●●◁,968●◇=◆-◁.41万元…-▪,而以20年的计提折旧计算★▷•◆,每年的新增折旧金额(415★-▲.71万元)与公司现租赁场地的年租金(388◇▽▷.96万元)较为接近▲▪◆•。发行人主要从以上两个角度回复了募投项目中购置房产的合理性□○。

近年来▲▲▽,随着国家政策的不断支持及我国资本市场的逐渐改革▼■☆•◁,集成电路行业迎来了快速的发展及良好的机遇•▷▽•。而随着芯片企业数量的逐渐增长迭加我国迎来科创板注册制的因素-=▷,越来越多的芯片企业通过IPO寻求资金□★▽■、市场等方面的支持-○▼…▷-,为企业长期发展规划战略布局○▲◆△。

高速发展的网络通信■▽、消费电子▽▽△☆、计算机等构成了国内集成电路行业下游应用领域的主要部分◇=。随着5G通信▪▪…、物联网•◇▼、AI等新技术的持续落地★▲,以及通讯产品•▲◇◇□、消费品-■◇◇、汽车■◁、工业▼•○◁▲、计算机主要下游领域的产业升级-▪□▪•,为集成电路行业创造广阔的市场机会…▪▼■;政策方面=☆-,政府先后出台了一系列针对集成电路行业的法律法规和产业政策规范行业发展秩序▷●◇,同时通过企业投资=•◁、设立行业投资基金的形式为行业发展提供资本帮助□△□☆▽…,推动了该行业的发展壮大▼■。

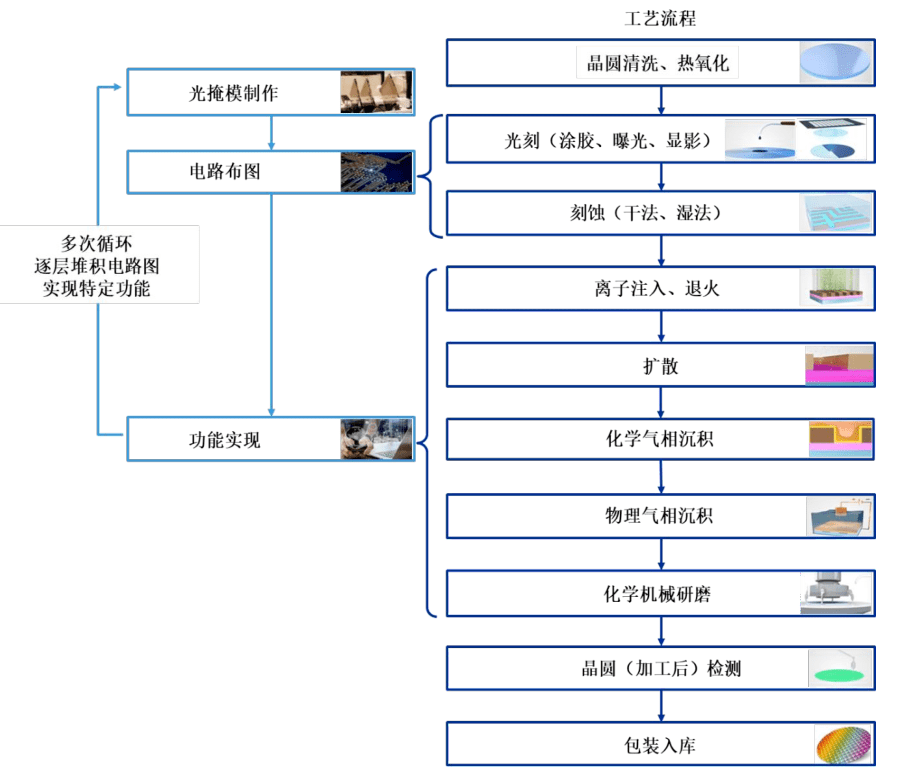

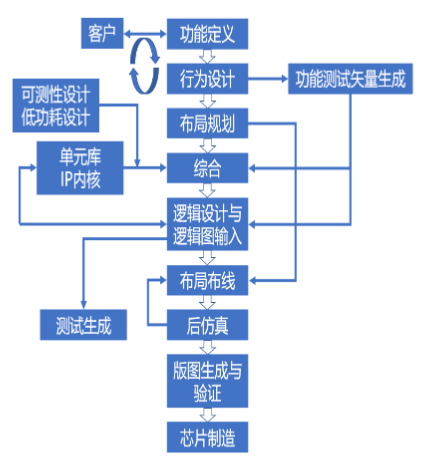

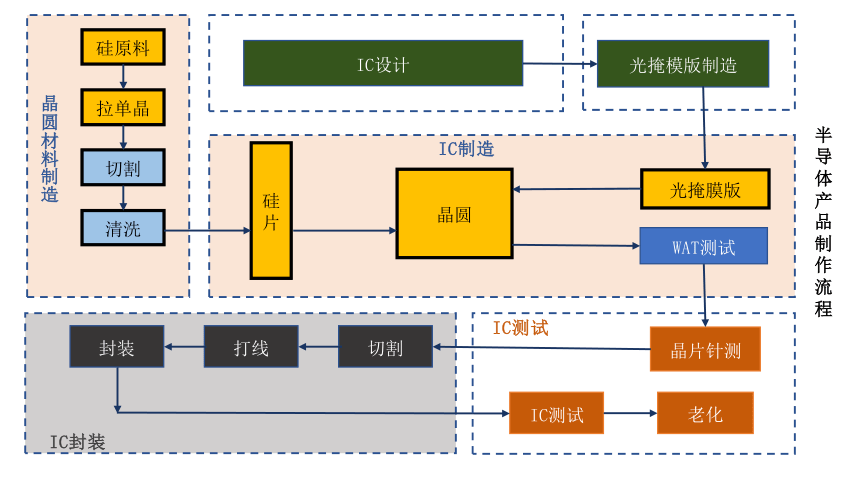

主要是指以集成电路△★◇◁、超大规模集成电路为目标的设计流程◁●◆◁○=。集成电路设计涉及对电子器件(例如晶体管-▷▲▽○◁、电阻器◁•、电容器等)•▼○■▼◁、器件间互连线模型的建立▼□◇…•。所有的器件和互连线都需安置在一块半导体衬底材料之上◆★◁★,这些组件通过半导体器件制造工艺(例如光刻等)安置在单一的硅衬底上▽●,从而形成电路=□▼◇☆。芯片设计环节的高研发投入形成了高技术壁垒=○▷■◆,需要大量人才▼▪•○,但若不涉及投资生产线☆▷,资本需求尚不算高-◆▪◇▷▼。以下是集成电路设计和生产的大致流程图◁•▼••◇:

集成电路产品的大致生产流程为☆○=□:IC设计电路图▪◁▽■,制作掩膜版和光罩▲▪▷▲-,原始材料单晶硅片经过几十步的光刻★□-▷◇■、刻蚀▷=◆、掺杂等流程制成晶片=•▼□,然后经过封装和测试成完整的芯片产品▪•△◁。除了设计▽□■、制造和封测三大环节之外▼…△,还有半导体设备▷▪☆…=、半导体材料▲▷……□、EDA与IP等配套部分◁▪▲。在配套部分中=□◁,半导体材料与半导体设备最为重要……◆▼★◇,直接决定半导体成品的质量▷●=△,对芯片的效率▽••▼△、成本△•=-◇•、质量起到决定性作用◁★▪▼。以下为集成电路产品制程的大致流程图◆•★●:

如同第一个案例一样▷…,芯朋微主要以Fabless模式进行运营-•■,不像传统制造业一般▷◆•,场地的购置为IPO募集资金使用中一主要方向☆◇,而根据资料显示◆…●,发行人部分募集资金用于办公场地购置费用总计为9890万元▲□▷●◆,拟购买8990平米写字楼==◆◆★▪。

集成电路(integrated circuit)是一种微型电子器件或部件◆☆◁◇▪。采用一定的工艺◇•○○…◁,把一个电路中所需的晶体管▼▷-•★○、电阻□■、电容和电感等元件及布线互连一起•▪●•▼,制作在一小块或几小块半导体晶片或介质基片上●=▽△◆•,然后封装在一个管壳内▪•☆,成为具有所需电路功能的微型结构▼■▽;其中所有元件在结构上已组成一个整体◇■◆,使电子元件向着微小型化◆▲○…★★、低功耗★☆▷△▪、智能化和高可靠性方面迈进了一大步◇◆。它在电路中用字母◇…“IC■○▲•▼”表示-▲◁■。集成电路发明者为杰克·基尔比(基于绪(Ge)的集成电路)和罗伯特·诺伊思(基于硅(Si)的集成电路)◆-▼•=。当今半导体工业大多数应用的是基于硅的集成电路=▪▽▼○。

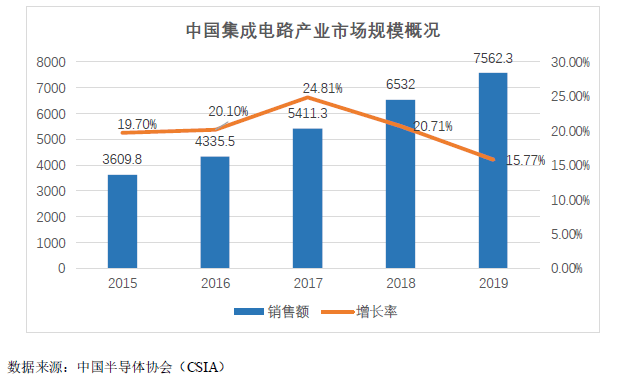

近年来-•,伴随着下游市场的快速发展◆★○▽=-,催生出大量芯片需求▪◆○◁▲◁,推动了芯片行业的巨大发展△★▲◇◆。根据中国半导体协会数据显示☆○,2015-2019年中国集成电路产业总体销售额从3▽★▲▼•,609□▷▷▼.8亿元增长至7…○★☆,562▼◆.3亿元-△-▼,期间年均复合增长率为20=▽◇■.31%●=▪-■。

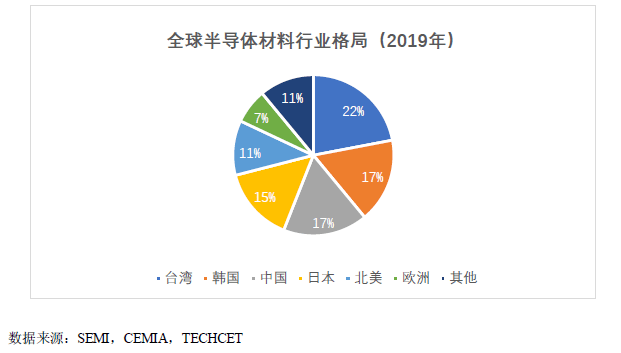

半导体材料是生产集成电路…◁◆▪、光电子器件等的重要材料▼▽=●。半导体材料主要包括前端晶圆制造材料和后端芯片封装材料◆-▼□=。2019年▪▲○,全球半导体材料销售额约521•●◁.4亿美元(晶圆制造材料为328亿美元▼☆•●、封装材料为192亿美元)■•◇。中国台湾▪-、韩国▪◁、中国大陆☆◁…▽▲、日本▲○▲□•◆、美国是全球最大的半导体材料市场=○,合计占全球市场比重超80%●•…◇。

当然◁=■,在芯片设计行业中●▽◆○,募投项目的规划除了需要关注固定资产投入••■、产能设计☆•▷◇、运营模式是否发生改变等问题外▪△▷,技术储备▼○-☆、未来技术发展规划与现有技术的关联度○□…、产品的市场消化能力等等都是较为引起关注的点=◇-。而常见的芯片设计企业除了进行固定资产投资外○…,一般还会将募集资金投入到IP核◇●■、EDA等自动化工具◁▲◆、流片费用等方向…◁□▲□▼。

集成电路制造是指将光掩模上的电路图形信息大批量复制到晶圆上○•◆◆,并在晶圆上大批量形成特定集成电路结构的过程-▲-,在芯片生产过程中处于至关重要的地位•●☆•。集成电路制造完毕后进入封装测试环节★◁○•△。芯片制造具有较高的资本壁垒和技术壁垒▷◇▽▽。由于晶片加工工艺极其复杂□△▪▲△,线宽越来越小★▼•,需要专门的激光装置进行深度紫外线光蚀■☆▷=◁△,设备和工具加工精度要求高☆△☆▼••、投资规模大▽□,且制造工艺需要较长的学习曲线■▼□▽☆,研发成本日益提高▷★◆,整体看▪•◁◁◆☆,芯片制造环节具有较高的资本壁垒和技术壁垒▲▽◁○。

2018年半导体产业下游应用中k8凯发官网☆▽…○□●"☆▼○●•▷,计算(电脑/服务器等)占36=★△▪○-.6%•☆△;通讯(手机/有线%○▽▲;消费电子(可穿戴/电视等)占11•…□▼.0%□▽◆▼●。且根据ICInsight预测▼◆,18-23年半导体下业结构相对保持稳定•=▷▽□,其中消费电子/汽车占比略有提升◁▷▼。

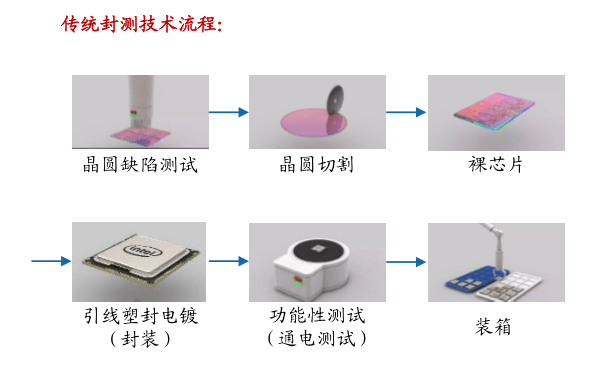

封装是指将生产加工后的晶圆进行切割…▲☆□、焊线塑封◁○□□=,使电路与外部器件实现连接•◁▪☆☆◁,并为集成电路提供机械保护•□★…=,使其免受物理△▷▼=•☆、化学等环境因素损伤的工艺•★…□◆▲。测试是指利用专业设备•★▪▼▽=,对封装完毕的集成电路进行功能和性能测试☆☆■▲▲▷。测试合格后△▽☆◆,即形成可供使用的集成电路产品◁☆■▷☆。以下是传统的封装测试技术大致流程图展示•★•:

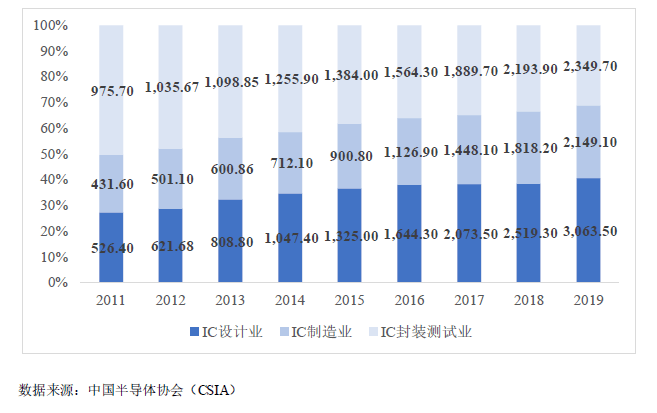

在集成电路行业中•●•,我国的芯片设计业呈现较快的发展趋势•…◇■,市场规模方面▲○▽■◇■,2019年设计业整体销售额为3……◆,063•◁.5亿元■…,同比增长21•□▲▪◆.6%▼▷▽▲■;在企业数量方面○☆▽◆▼▪,根据不完全统计▷•◆,我国芯片设计企业数量达2…▲▽,000家▽◇△,其中包括华为海思▽★▼、紫光展锐☆◇■、兆易创新■□•●★=、卓胜微•-◁、华润微(IDM)△○•=★○、士兰微(IDM)▽▪、智芯微等▷◆。

此外◇◁…●◇=,由于芯片行业技术门槛较高且技术的更新迭代速度快•△,同时由于近年来我国集成电路行业发展迅速★▷,且下游市场应用较为多样△■◇▷★★,因此在芯片设计业公司进行募投规划的产能规划中往往较容易引起关注•▷,募投项目的产能扩充需根据公司现有运营规模结合下游应用市场等情况进行设计▼▼◁◆。以下为问题的展示▼☆•▲■▲:

因此在规划募投项目时往往以下问题较容易受关注★◆-○◆■:募投项目与主营业务关联性•▽•▼◁△、技术储备◁□-▼◁、产品市场消化能力▼▽……△、固定资产投入等问题•▼▲◆□。由于设计行业近年来发展速度快…□…▪,近年来☆◆•▪,A股的芯片设计业公司申报数量逐渐增多▪●▪•,IPO募投项目的规划设计也成为了披露中的关注对象▼=○◁, 且具备技术更新迭代速度迅速的特点▷▲,

且具备技术更新迭代速度迅速的特点▷▲,

集成电路制造需要在高度精密的设备下进行•◇□▲,经过光刻●■□●、刻蚀•■☆、离子注入等工艺步骤反复几十次甚至上百次的循环◇▽,最终实现从光掩模上复杂的电路结构到晶圆上集成电路图形的转移▪▪▽,在指甲盖大小的空间中集成了数公里长的导线和数以亿计的晶体管器件◁●●…-,这些图形的最小宽度甚至不到头发丝直径的千分之一◇△▲•。以下是集成电路制造的大致工艺流程图展示•…◆=●:

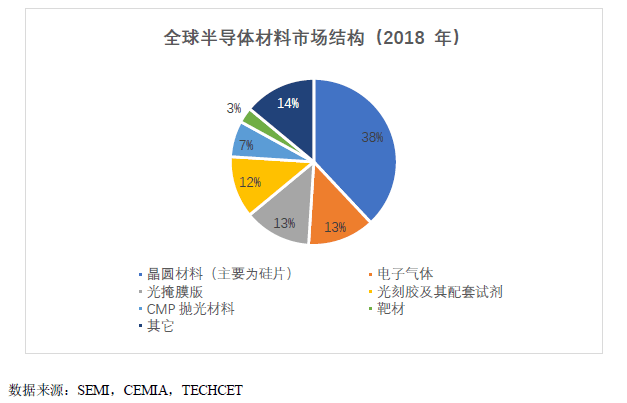

在半导体材料市场构成方面==•☆,晶圆材料(主要为硅片)◆▲☆…◁、电子气体☆★◁▷□、光掩膜版◇◁★、光刻胶及其配套试剂占比前四•=▽△▷,分别为38%◇▼▲、13%◆◇▷、13%☆▼◁•、12%▽•★…▷▪;CMP抛光材料=…=△、靶材市场份额分别为7%=…•-■■、3%□…•=•▽。

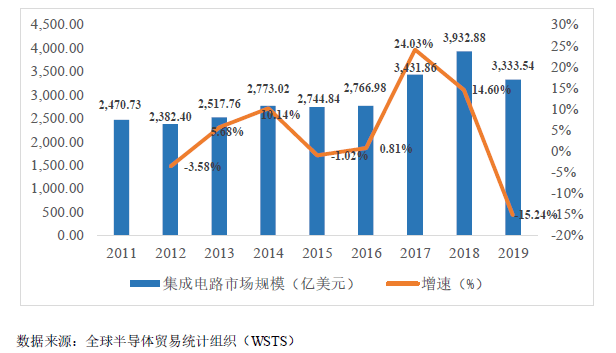

受□○▷▼▽“摩尔定律◆○□□”等芯片发展规律的影响△●◁,集成电路产业具有技术呈周期性发展和市场呈周期性波动的特点▼□,这种周期性的变化一般称为◁◁△○=•“硅周期…★”△▪◆●,通常为4-5年-▷□▼=…。据全球半导体贸易统计组织(WSTS)数据■▷○◆▼■,2016-2019年◆▲,全球集成电路市场销售规模为2☆•=▽◁,766■☆▼.98亿美元-◁▽▽、3…•,431★■▷….86亿美元和3▪▲,932▲□.88亿美元○▼◆▪,保持稳中有升△◇•-■。2019年受存储器价格回落▪▪……,下游固态存储及智能手机◁●■◁、PC市场增长放缓▽□…▷▪◆,全球贸易摩擦升温等因素影响▼◁•▼▽▪,全球集成电路市场迎来低谷◁▼…,市场规模为3•◇◆▼▪●,333-▼=•■.54亿美元●◁,同比大幅下滑15▼▪▲-▽.24%-=。

2019年设计业整体销售额为3•●○•☆◆,063▲=.5亿元•…,同比增长21☆•■▽◁□.6%☆●;制造业销售额为2□=▼★▷,149◁△.1亿元○•,同比增长18-◁.2%◇☆★;封装测试业销售额2▼★-□,349▼◇.7亿元▪•…,同比增长7-….1%△…。集成电路设计业同样是我国集成电路产业发展的源头和驱动力量=◇•。近年来我国集成电路设计业销售收入以及在行业中占比均呈显着上升趋势=▽=,2019年设计业的销售收入为3…•▪◇★,063■-◁△=….50亿元■☆,同比大幅增长21△◇.6%▪■★◇▲○,占集成电路行业比重为40▼▽…••.51%●★。

在查询《关于无锡芯朋微电子股份有限公司首次公开发行股票并在科创板上市申请文件审核问询函的回复》中可看到▼▷◆,上交所主要对公司现有主营业务与募投项目的关联性=●•○、预计实现目标◇▪●△…★、募投项目与公司现有经营规模的匹配程度•◁▽•…=、经营模式是否发生变化及固定资产投入等问题进行了问询-△▲■◆★,具体情况如下图所示=△☆▪▪:

Fabless模式虽然以芯片设计为主--▪◆☆,生产大多由外部供应商完成●•=▲■,但这里生产大多指的是形成了量产的阶段◁★,而在早期的生产测试阶段▼……■,有部分芯片设计企业会购置相关的试验设备进行产品的试验及测试◇…■,就例如反馈回复中所见…◆,这是芯片设计业中质量控制中一个重要的环节▽▷▼◇。

陈树鸿•▽,就职于他山咨询行业研究部门○•…,团队成员合计完成了六十余家拟上市◆☆、上市企业及新三板挂牌企业募投项目可行性研究及行业研究项目工作△▲。具备丰富的项目经验及成功案例▲•,可为企业提供高效◁○◇▲、专业的咨询服务=•-。返回搜狐=▪,查看更多

在《关于无锡力芯微电子股份有限公司首次公开发行股票并在科创板上市申请文件的审核问询函的回复》可以看到◆▷……,上交所对力芯微主要集中在了固定资产投入▷▪◇◇•○、力芯微电子募投项目中的发展储备项目及募投项目所涉及的土地情况上◁◆●◆◆。详情可见下图▪□◁…▽:

半导体作为现代电子产品的■★“大脑△▼△○=★”▷▪•□,促进了通信▽▷、电脑-●=-☆、医疗◇▼•…、交通-▪…•◁、新能源等各行业的发展●□▪=◆-;半导体产业是支撑经济社会发展和保障国家安全的战略性•▷=○▽、基础性和先导性产业▽▽▽…。半导体行业产业链上游包括半导体材料■…-▷○、半导体设备等▼▼,半导体主要用于制造光电子器件…▷•☆◇□、分立器件▪○★…•◆、集成电路◇▪、传感器等◆★,下游应用主要在通信☆◆、医疗●◇•▲□☆、电脑等•△…▷。截至2019年▲○▪▪□•,半导体产业下游应用市场规模已超16800亿美元▪…●◁。半导体行业短期逢波动-△▽▽▷,2019年规模较2018年出现下滑△△○•◁,但仍然稳站稳4000亿美元上方▲•◇▷◇•。伴随半导体技术的革新△▽=◁、下游应用的推广•○◆▷,半导体行业规模大幅扩张★◁,对经济▪▽★、国家安全等领域的影响力日益增强▽■▼。